[더스탁=고명식 기자] 반도체 산업은 자본 집약적이며 설비 중심적이다. 초미세 반도체 생산이 가능한 ASML의 차세대 장비는 1대 가격이 무려 5000억원을 호가한다. 게다가, 돈이 있다고 살 수 있는게 아니다. 순서와 선택을 기다려야 한다.

ASML이 공식 엑스(옛 트위터)를 통해 첫번째 High NA EUV 시스템이 출하돼 인텔의 미국 오레곤 팹에 적용된다고 밝혔다. 인텔은 ASML의 '하이 NA EUV' 초도 물량 6대를 모두 확보해 2나노 이하 초미세 반도체 시장에 선두에 서게 된 것으로 보인다.

'하이 NA EUV 장비'는 2나노 이하 초미세 공정에 필수적인 장비로, 반도체 업계의 '게임체인저'로 불린다. 기존 EUV 장비로는 2나노 이하 공정 구현이 어렵다. 특히, 하이 NA EUV는 반도체 칩의 성능과 전력 효율을 크게 향상시킬 것으로 기대된다.

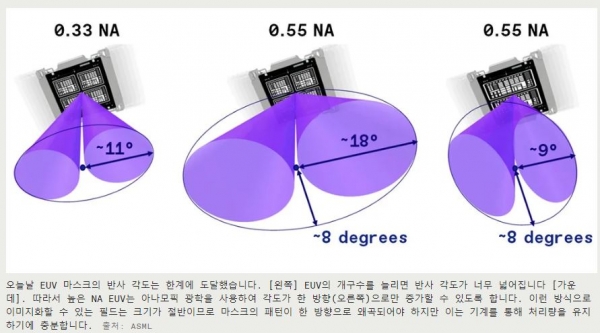

하이 NA(numerical aperture) EUV 장비는 EUV 장비에서 빛을 받아 들이거나 내보내는 렌즈의 상대적 크기를 0.33에서 0.55로 끌어올렸다. 이에 따라, 초미세 회로를 웨이퍼에 새길 수 있다. 빛의 집광 능력이 높아 훨씬 세밀한 반도체 회로를 그릴 수 있기 때문에 2nm 이하 초미세 공정에서 하이 NA EUV는 필수장비로 여겨지고 있다.

ASML의 첫 번째 '하이 NA EUV' 장비를 공급받게 된 인텔은 내년 상반기 20A(2nm급) 제조공정을 본격화하고 같은 해 하반기에는 18A(1.8nm급) 반도체 제조에 시동을 건다는 계획이다. 삼성과 TSMC는 2025년말까지 2나노급 칩 생산을 목표로 하고 있지만 현재까지 ASML의 '하이 NA EUV' 장비 공급은 불투명한 상황이다.

최근 삼성전자가 7억 유로(한화 약 1조원)를 투자해 ASML과 협력해 국내에 극자외선 공동 연구소 설립을 추진하고 있는 것은 '0.55 하이 NA' 이후 0.75로 확대될 '하이퍼 NA EUV' 선점을 위한 사전 포석이라는 분석도 있다. 0.55NA는 인텔에 선두를 줬지만 0.75에서 선두를 잡자는 것이다. ASML 측은 하이퍼 NA EUV 장비 생산까지는 향후 약 10년 정도가 소요될 것으로 예상하고 있다.

글로벌 반도체 산업은 인텔과 삼성, TSMC와 마이크론 그리고 SK하이닉스 등이 불꽃 경쟁을 벌이고 있다. EUV 노광장비는 ASML이 전세계 독점 생산하며 3nm 이상 시스템반도체와 10nm급 D램 제조에 필수적이다. 삼성전자와 TSMC, 인텔과 SK하이닉스,마이크론 등이 EUV 노광장비를 사용하는 기업들이며 이들 모두가 0.55 NA EUV 장비를 ASML에 요청한 상태다. 물론, 이중에서 인텔만이 올해와 내년 장비를 공급 받아 설치와 운영이 가능한 상황이다.

ASML 측에 따르면, 양산용 '하이 NA' 장비는 2025년부터 본격적인 상용화가 추진된다. 정확한 규모는 아직 공식적인 내용이 없다. 일각에서는 2024년 연간 5대 가량의 '하이 NA' 생산이 가능하다는 분석도 있지만, 이베스트투자증권 지용호 연구원은 2025~2026년 ASML의 '하이 NA EUV' 출고량이 20대 수준이 될 것으로 예상하고 있다. ASML 측은 계획대로 준비가 된다면 2025년 20대, 2026년 40대 이상 생산도 가능할 것으로 전망하고 있다.

인텔이 ASML의 '하이 NA'의 첫 수혜자가 될 것이라는 것은 이미 확정돼 있었던 것으로 보인다. 올해 9월 ASML의 CEO 피터 웨닝크는 로이터와의 인터뷰에서 "인텔이 파일럿 High-NA 스캐너의 알파 고객이 될 것이다. 올해 말에 장비가 인텔 측에 도착하면 개발자와 엔지니어들이 인텔의 생산공정에 맞춰 장비의 설정과 세팅을 조정하는 과정이 필요할 것"이라고 밝혔다.

기존 EUV 장비로도 다중 패터닝 기술을 이용하면 2나노 이하 반도체 생산이 가능은 하다. 그러나 공정이 많아지고 복잡하며 비용도 많이 들어간다. 또 불량률이 높아 '0.55 하이 NA' 도입이 필수적이다. 인텔은 6대의 '하이 NA EUV'를 확보했고 이중 첫 제품이 출하됐다. 반면 삼성과 TSCM 등 나머지 반도체 기업들은 2025년 이후에나 장비 확보가 가능하기 때문에 2년 가량의 기술 격차는 불기피해 보인다.

인텔은 공정 기술과 제품 포트폴리오 측면에서 다른 기업들 보다 우위를 점하고 있다. 특히, 이번 '0.55nm 하이 NA' 장비 도입으로 경쟁 기업 보다 한발 앞서게 될 것으로 보인다. 삼성전자는 메모리 반도체 분야에서 우위에 있고 TSMC는 팹리스 고객사를 위한 반도체 생산을 주력하고 있다. SK하이닉스는 메모리 반도체 분야에서 삼성전자와 경쟁하고 있는데 나노공정 측면에서는 후발주자에 속한다. 마이크론은 메모리 반도체 분야에서 삼성전자와 경쟁하고 있다. 마이크론은 2023년 7월에 3나노 DRAM과 NAND 플래시를 양산하기 시작했고 2025년에는 2나노 DRAM과 NAND 플래시를 양산한다는 계획이다.